# Data Structure Identification from Executions of Pointer Programs

Thomas Rupprecht

**41** Schriften aus der Fakultät Wirtschaftsinformatik und Angewandte Informatik der Otto-Friedrich-Universität Bamberg

Contributions of the Faculty Information Systems and Applied Computer Sciences of the Otto-Friedrich-University Bamberg

Schriften aus der Fakultät Wirtschaftsinformatik und Angewandte Informatik der Otto-Friedrich-Universität Bamberg

Contributions of the Faculty Information Systems and Applied Computer Sciences of the Otto-Friedrich-University Bamberg

Band 41

# Data Structure Identification from Executions of Pointer Programs

Thomas Rupprecht

Bibliographische Information der Deutschen Nationalbibliothek Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliographie; detaillierte bibliographische Informationen sind im Internet über

http://dnb.d-nb.de/abrufbar.

Diese Arbeit hat der Fakultät Wirtschaftsinformatik und Angewandte Informatik der Otto-Friedrich-Universität Bamberg unter dem Titel "Data Structure Identification from Executions of Pointer Programs" als Dissertation vorgelegen.

1. Gutachter: Prof. Dr. Gerald Lüttgen, University of Bamberg

2. Gutachter: Prof. Dr. Thomas Noll, RWTH Aachen University

Tag der mündlichen Prüfung: 7. November 2019

Dieses Werk ist als freie Onlineversion über das Forschungsinformationssystem (FIS; fis. uni-bamberg.de/) der Universität Bamberg erreichbar. Das Werk – ausgenommen Cover, Zitate und Abbildungen – steht unter der CC-Lizenz CC-BY.

Lizenzvertrag: Creative Commons Namensnennung 4.0 http://creativecommons.org/licenses/by/4.0

Herstellung und Druck: docupoint, Magdeburg Umschlaggestaltung: University of Bamberg Press

© University of Bamberg Press, Bamberg 2020 http://www.uni-bamberg.de/ubp/

ISSN: 1867-7401

ISBN: 978-3-86309-717-2 (Druckausgabe) eISBN: 978-3-86309-718-9 (Online-Ausgabe)

URN: urn:nbn:de:bvb:473-irb-473250

DOI: http://dx.doi.org/10.20378/irb-47325

### **Acknowledgments**

I want to thank Dr. David White and Prof. Gerald Lüttgen for making this dissertation thesis possible. Further I am very glad about the collaboration with Prof. Herbert Bos together with Dr. Xi Chen from the VU Amsterdam in the Netherlands and Dr. Tobias Mühlberg from the KU Leuven in Belgium.

However, this work would not have come into existence without the great support and patience throughout the years from my parents and my wife. Thank you!

I also want to thank all my colleagues from the Software Technologies Research Group for lots of interesting discussions and good times, e.g., the country side tour will (mostly) be unforgotten and your wedding gift still resides prominently in our living room. Special thanks to Jan Boockmann from our group, for being an invaluable help on so many occasions.

Additionally, I'm happy about my friends from my home town Hundelshausen and the neighbouring Altmannsdorf, who went with me through good and bad times since I was born. Further, I want to list some great human beings I have met during my life that are worth mentioning for reasons they know best themselves (in order of appearance in my life): Peter Hofmann, Daniel Finster, Christian Wiegand, Leslie Polzer and Tobias Zeck.

Finally, I want to give my appreciation to some outstanding individuals that made or still make music that motivates me: Kevin, Lemmy, James.

#### **Abstract**

The reverse engineering of binaries is a tedious and time consuming task, yet mandatory when the need arises to understand the behaviour of a program for which source code is unavailable. Instances of source code loss for old arcade games<sup>1</sup> and the steadily growing amount of malware<sup>2</sup> are prominent use cases requiring reverse engineering. One of the challenges when dealing with binaries is the loss of low level type information, i.e., primitive and compound types, which even state-of-the-art type recovery tools often cannot reconstruct with full accuracy. Further programmers most commonly use high level data structures, such as linked lists, in addition to primitive types. Therefore detection of dynamic data structure shapes is an important aspect of reverse engineering. Though the recognition of dynamic data structure shapes in the presence of tricky programming concepts such as pointer arithmetic and casts – which are both fundamental concepts to enable, e.g., the frequently used Linux kernel list<sup>3</sup> – also bring current shape detection tools to their limits.

A recent approach called Data Structure Investigator (DSI)<sup>4</sup>, aims for the detection of dynamic pointer based data structures. While the approach is general in nature, a concrete realization for C programs requiring *source code* is envisioned as programming constructs such as type casts and pointer arithmetic will stress test the approach. Therefore, the first research question addressed in this dissertation is whether DSI can meet its goal in the presence of the sheer multitude of existing data structure implementations. The second research question is whether DSI can be opened up to reverse engineer C/C++ binaries, even in the presence of type information loss and the variety of C/C++ programming constructs.

Both questions are answered positively in this dissertation. The first is answered by realizing the DSI source code approach, which requires detailing fundamental aspects of DSI's theory to arrive at a working implementation, e.g., handling the consistency of DSI's memory abstraction and quantifying the interconnections found within a dynamic pointer based data structure, e.g., a parent child nesting scenario, to allow for its detection. DSI's utility is evaluated on an extensive

$<sup>^{1}</sup>http://kotaku.com/5028197/sega\text{-}cant\text{-}find\text{-}the\text{-}source\text{-}code\text{-}for\text{-}your\text{-}favorite\text{-}old\text{-}school-arcade\text{-}games}$

<sup>&</sup>lt;sup>2</sup>https://www.av-test.org/en/statistics/malware/

<sup>&</sup>lt;sup>3</sup>https://github.com/torvalds/linux/blob/master/include/linux/list.h

<sup>&</sup>lt;sup>4</sup>SWT Research Group, University Bamberg, DFG-Project LU 1748/4-1

benchmark including real world examples (libusb<sup>5</sup>, bash<sup>6</sup>) and shape analysis<sup>7,8</sup> examples. The second question is answered through the development of a DSI prototype for binaries (DSIbin). To compensate for the loss of perfect type information found in source code, DSIbin interfaces with the state-of-the-art type recovery tool Howard<sup>9</sup>. Notably, DSIbin improves upon type information recovered by Howard. This is accomplished through a much improved nested struct detection and type merging algorithm, both of which are fundamental aspects for the reverse engineering of binaries. The proposed approach is again evaluated by a diverse benchmark containing real world examples such as, the VNC clipping library, The Computer Language Benchmarks Game and the Olden Benchmark, as well as examples taken from the shape analysis literature.

In summary, this dissertation improves upon the state-of-the-art of shape detection and reverse engineering by (i) realizing and evaluating the DSI approach, which includes contributing to DSI's theory and results in the DSI prototype; (ii) opening up DSI for C/C++ binaries so as to extend DSI to reverse engineering, resulting in the DSIbin prototype; (iii) handling data structures with DSIbin not covered by some related work such as skip lists; (iv) refining the nesting detection and performing type merging for types excavated by Howard. Further, DSIbin's ultimate future use case of malware analysis is hardened by revealing the presence of dynamic data structures in multiple real world malware samples.

In summary, this dissertation advanced the dynamic analysis of data structure shapes with the aforementioned contributions to the DSI approach for source code and further by transferring this new technology to the analysis of binaries. The latter resulted in the additional insight that high level dynamic data structure information can help to infer low level type information.

<sup>&</sup>lt;sup>5</sup>http://libusb.info/

<sup>&</sup>lt;sup>6</sup>https://www.gnu.org/software/ bash/

<sup>&</sup>lt;sup>7</sup>Predator: http://www.fit.vutbr.cz/research/groups/verifit/tools/predator/

<sup>&</sup>lt;sup>8</sup>Forester: http://www.fit.vutbr.cz/research/groups/verifit/tools/forester/

<sup>&</sup>lt;sup>9</sup>http://www.cs.vu.nl/ herbertb/papers/dde\_ndss11-preprint.pdf

#### Zusammenfassung

Reverse Engineering von Binärcode ist eine schwierige und zeitaufwändige Tätigkeit, die jedoch unabdingbar ist, wenn das Programmverhalten verstanden werden muss, ohne dass Quelltext zur Verfügung steht. Fälle von Quelltextverlust für alte Computerspiele<sup>10</sup> und die stetig wachsende Anzahl von Schadsoftware<sup>11</sup> sind daher prominente Anwendungsfälle für Reverse Engineering. Eine der Herausforderungen bei der Analyse von Binärcode ist der Verlust von Typinformationen, wie zum Beispiel primitiven und komplexen Datentypen. Oftmals können diese Typinformationen von den aktuellen Werkzeugen zur Typrückgewinnung, die den Stand der Technik repräsentieren, nicht vollumfänglich und korrekt rekonstruiert werden. Weiterhin verwenden Programme zusätzlich zu den primitiven und komplexen Datentypen meist höhere dynamische Datenstrukturen, wie zum Beispiel verkettete Listen. Daher ist die Erkennung der Form von dynamischen Datenstrukturen ein wichtiger Aspekt des Reverse Engineerings. Wobei die Erkennung der Formen dynamischer Datenstrukturen im Kontext von schwierigen Programmierkonzepten, wie Zeigerarithmetik und Typumwandlungen - beides fundamentale Konzepte um zum Beispiel die häufig verwendete Linux Kernel Liste<sup>12</sup> zu implementieren – aktuelle Werkzeuge zur Formenerkennung von dynamischen Datenstrukturen an ihre Grenzen bringen.

Ein aktueller Ansatz (DSI<sup>13</sup>) zielt auf die Erkennung von dynamischen zeigerbasierten Datenstrukturen ab. Der Ansatz ist generell gehalten, wobei eine konkrete Umsetzung für C-Programme unter Verwendung von Quelltext durchgeführt wird, da Typumwandlungen und Zeigerarithmetik als Bestandteil des C-Sprachumfangs einen Stresstest für den Ansatz darstellen. Daher ist die erste Forschungsfrage innerhalb dieser Dissertation, ob DSI seinen eigenen Anforderungen auch unter der schieren Vielzahl an existierenden Datenstrukturimplementierungen gerecht wird. Die zweite Forschungsfrage behandelt, ob Reverse Engineering von C/C++ Binärcode mit DSI erschlossen werden kann, trotz des Verlusts von Typinformationen und der Vielzahl von C/C++ Programmierkonstrukten.

Beide Forschungsfragen werden positiv innerhalb dieser Dissertation beantwortet. Die erste Frage wird durch eine Umsetzung des DSI Quelltext-Ansatzes er-

<sup>&</sup>lt;sup>10</sup>http://kotaku.com/5028197/sega-cant-find-the-source-code-for-your-favorite-old-school-arcade-games

<sup>&</sup>lt;sup>11</sup>https://www.av-test.org/en/statistics/malware/

<sup>&</sup>lt;sup>12</sup>https://github.com/torvalds/linux/blob/master/include/linux/list.h

<sup>&</sup>lt;sup>13</sup>SWT Research Group, University Bamberg, DFG-Project LU 1748/4-1

forscht. Dies umfasst die Ausdetaillierung von fundamentalen Aspekten der DSI Theorie um eine funktionsfähige Implementierung zu erreichen, zum Beispiel die Erhaltung der Konsistenz der Speicherabstraktion von DSI und die Quantifizierung von Verbindungen innerhalb einer zeigerbasierten dynamischen Datenstruktur, wie zum Beispiel einer Eltern-Kind-Beziehung, um eine Erkennung solcher Verbindungen zu ermöglichen. Die Nützlichkeit von DSI wird an Hand eines umfassenden Testsets untersucht, das unter anderem Praxisbeispiele (libusb¹⁴, bash¹⁵) und Beispiele der Forschungsrichtung der Shape Analysis¹⁶,¹⁷ beinhaltet.

Die zweite Forschungsfrage wird durch die Entwicklung eines DSI Prototypen für Binärcode (DSIbin) beantwortet. Um den Verlust von perfekten Typinformationen, die bei der Verwendung von Quelltext verfügbar sind, zu kompensieren, wird DSIbin mit Howard<sup>18</sup> kombiniert, einem Werkzeug zur Typrückgewinnung, das den aktuellen Stand der Technik in diesem Bereich repräsentiert. Insbesondere verbessert DSIbin zusätzlich die von Howard zur Verfügung gestellten Typinformationen durch eine immens verbesserte Erkennung eingebetteter Strukturen sowie der Typzusammenführung. Beide Problemstellungen sind grundlegende Aspekte für das Reverse Engineering von Binärcode.

Der vorgeschlagene Ansatz wird ebenso durch ein manigfaltiges Testset untersucht, das unter anderem Praxisbeispiele umfasst, wie die "VNC clipping library", "The Computer Language Benchmarks Game", den "Olden Benchmark" und Beispiele aus der Shape Analysis Literatur.

Diese Dissertation verbessert den aktuellen Stand der Technik für die Erkennung von Datenstrukturen und des Reverse Engineering durch (i) die Umsetzung und Evaluation des DSI Ansatzes, was Beiträge zur Theorie von DSI beinhaltet und in einem DSI Prototypen resultiert; (ii) die Öffnung von DSI zur Analyse von C/C++ Binärcode um DSI auf das Reverse Engineering zu erweitern, was ebenfalls in einem Prototypen für DSIbin resultiert; (iii) die Behandlung von Datenstrukturen mit DSIbin, die bisher von einiger verwandter Literatur nicht abgedeckt wurden, wie zum Beispiel Skip-Listen; (iv) eine Verfeinerung der Erkennung von eingebetteten Strukturen und die Zusammenführung von Typinformationen die von Howard ermittelt wurden. Weiterhin wird der Anwendungsfall der Analyse von Malware für DSIbin im Bereich des Future Work gestärkt, indem die Verwendung von dynamischen Datenstrukturen in verschiedenen realen Malware Stichproben nachgwiesen wird.

Zusammenfassend erweitert diese Dissertation die dynamische Analyse von dynamischen Datenstrukturen gemäß den zuvor aufgeführten Beiträgen zu dem DSI Ansatz für Quelltext sowie durch den Transfer dieser neuen Technologie auf

<sup>&</sup>lt;sup>14</sup>http://libusb.info/

<sup>&</sup>lt;sup>15</sup>https://www.gnu.org/software/bash/

<sup>&</sup>lt;sup>16</sup>Predator: http://www.fit.vutbr.cz/research/groups/verifit/tools/predator/

<sup>&</sup>lt;sup>17</sup>Forester: http://www.fit.vutbr.cz/research/groups/verifit/tools/forester/

<sup>&</sup>lt;sup>18</sup>http://www.cs.vu.nl/ herbertb/papers/dde\_ndss11-preprint.pdf

die Analyse von Binärcode. Letzteres führte zu der zusätzlichen Erkenntnis, dass Informationen von höheren dynamischen Datenstrukturen helfen können primitive Typinformationen abzuleiten.

## **Contents**

| 1 | Intro | oduction                                      | xxxi   |

|---|-------|-----------------------------------------------|--------|

|   | 1.1   | Source code: Research question and challenges | xxxiv  |

|   | 1.2   | Binary code: Research question and challenges | xxxvii |

|   | 1.3   | Structure of the dissertation                 | xl     |

|   | 1.4   | Methodology                                   | xli    |

|   | 1.5   | Project context and publications              | xli    |

| I | Dy    | namic data structures in C programs           | 1      |

| 2 | DSI   | on source code                                | 3      |

| 3 | State | e of the art                                  | 9      |

|   | 3.1   | MemPick                                       | 10     |

|   | 3.2   | DDT                                           | 11     |

|   | 3.3   | ARTISTE                                       | 12     |

|   | 3.4   | dsOli                                         | 13     |

|   | 3.5   | Laika                                         | 13     |

|   | 3.6   | Predator, Forester and ATTESTOR               | 14     |

|   | 3.7   | HeapDbg & Heapviz                             | 15     |

| 4 | Con   | sistency of memory abstractions               | 19     |

|   | 4.1   | Artificial memory events                      | 20     |

|   | 4.2   | Memory leak detection                         | 21     |

|   |       | 4.2.1 Memory leak detection tools             | 22     |

|   |       | 4.2.2 Memory leak detection algorithms        | 23     |

|   |       | 4.2.3 DSI's memory leak detection algorithm   | 24     |

|   |       | 4.2.4 CIL: Creation of temporary pointers     | 28     |

|   | 4.3   | Benchmark                                     | 31     |

|   | 4.4   | Case study                                    | 34     |

| 5 | Stra  | nd connections                                | 45     |

|   | 5.1   | Related work                                  | 48     |

|   | 5.2   | Overlay strand connections                    | 49     |

|   |       | 5.2.1 Detecting an overlay connection         | 49     |

|   |       | 5.2.2 Quantifying an overlay connection       | 51     |

xiv Contents

|   |      | 5.2.3                 | Pseudocode for calculating overlay strand connections. |

|---|------|-----------------------|--------------------------------------------------------|

|   | 5.3  | Indire                | ct strand connections                                  |

|   |      | 5.3.1                 | Detecting an indirect strand connection                |

|   |      | 5.3.2                 | Pseudocode for calculating indirect strand connections |

|   | 5.4  | Entry p               | point connections                                      |

| 6 | Tem  | poral re <sub>l</sub> | petition                                               |

|   | 6.1  |                       | thm                                                    |

|   |      | 6.1.1                 | Main algorithm for temporal repetition                 |

|   |      | 6.1.2                 | Aligning ASG and FSG                                   |

|   |      | 6.1.3                 |                                                        |

|   |      | 6.1.4                 | Extending the ASG with new elements                    |

|   | 6.2  |                       | nary                                                   |

| 7 | Para | llelizatio            | on                                                     |

|   | 7.1  |                       | ilities for parallelization                            |

|   | 7.2  |                       | el implementation                                      |

|   | 7.3  |                       | marking                                                |

|   |      | 7.3.1                 |                                                        |

|   |      | 7.3.2                 | Computebox                                             |

|   |      | 7.3.3                 | Optimizations                                          |

| 8 | Ben  | chmarki               | ng                                                     |

|   | 8.1  |                       | iling the DSI benchmark                                |

|   |      | 8.1.1                 | Categorization of examples                             |

|   |      | 8.1.2                 | Discussion of additional benchmarks                    |

|   | 8.2  | The D                 | SI benchmark                                           |

|   |      |                       | First SLL and DLL examples                             |

|   |      | 8.2.2                 | Short running example                                  |

|   |      | 8.2.3                 | Skip list implementations                              |

|   |      | 8.2.4                 | Revealing unintended data structure semantics          |

|   |      | 8.2.5                 | Structurally complex examples                          |

|   |      |                       | Usefulness of DSI: Poor code readability               |

|   |      |                       | Usefulness of DSI: Huge code base                      |

|   |      | 8.2.6                 | DLL implementations                                    |

|   |      | 8.2.7                 | Nesting scenarios                                      |

|   |      | 8.2.8                 | Data structures on the stack                           |

|   |      | 8.2.9                 | Binary tree implementations                            |

|   |      | 8.2.10                | Limitations of DSI revealed by X.Org                   |

|   |      | 8.2.11                | Discussion of arrays and strands                       |

|   |      | 8.2.12                | Requiring semantics to reveal true shape               |

|   |      | 8.2.13                | Limitations of DSI revealed by tsort                   |

Contents xv

|    |       |          | Ambiguous nesting cases                                 |

|----|-------|----------|---------------------------------------------------------|

|    |       | 8.2.14   | Segmentation of event trace and convergence of evidence |

|    |       |          | counts                                                  |

|    |       |          | Removing parts from a data structure                    |

|    | 8.3   |          | tudy: Debugging with DSI                                |

|    | 8.4   | Summ     | ary of benchmarking                                     |

| 9  | Cond  | lusions  |                                                         |

| II | Dy    | namic    | data structures in object code                          |

| 10 | Dyna  | amic dat | ta structures in malware                                |

|    | 10.1  | Carber   | rp & Rovnix                                             |

|    |       |          | om, HellBot3 & Grum                                     |

|    |       |          | t                                                       |

|    | 10.4  | Conclu   | asions                                                  |

| 11 | DSI : | source c | code dependencies                                       |

| 12 | Data  | type re  | covery tools                                            |

|    |       | · -      | formats of the type recovery tools                      |

|    |       |          | Memory snapshots                                        |

|    |       |          | Binary code & byte code                                 |

|    | 12.2  | Recove   | ered type information                                   |

|    | 12.3  | Compa    | arison between Howard and Divine                        |

| 13 | Bina  | ry code  | instrumentation                                         |

|    | 13.1  |          | al overview of Pin                                      |

|    |       |          | Instrumentation and analysis routines                   |

|    | 13.2  |          | mentation details for DSIbin                            |

|    |       |          | Instrumentation of malloc and free                      |

|    |       |          | Startup and shutdown of the program under analysis .    |

|    |       |          | Tracking the stack and the heap                         |

|    |       | 13.2.4   | Modeling registers                                      |

| 14 |       |          | of Howard and DSIcore                                   |

|    |       |          | n: Combining Howard and DSIcore                         |

|    | 14.2  | Iechni   | cal details of DSIbin's binary frontend architecture    |

| 15 |       |          | ng of naive combination                                 |

|    | 15.1  |          | mark: General overview                                  |

|    |       | 15.1.1   | Dynamic data structure interconnections                 |

xvi

|     |         | 15.1.2  | Dynamic data structure obfuscation                         | 163 |

|-----|---------|---------|------------------------------------------------------------|-----|

|     |         | 15.1.3  | Allocations on the heap and the stack                      | 164 |

|     |         | 15.1.4  | Nested structs                                             | 165 |

|     | 15.2    | Discus  | sion of positive examples                                  | 165 |

|     | 15.3    | Discus  | sion of negative examples                                  | 167 |

|     |         |         | Loss of cyclicity property                                 | 167 |

|     |         |         | Changes in connections                                     | 168 |

|     |         | 15.3.3  | Obfuscation                                                | 169 |

|     |         | 15.3.4  | Conclusions                                                | 170 |

| 16  | Refin   | ement   |                                                            | 173 |

|     | 16.1    | Refine  | ment approach DSIref                                       | 173 |

|     | 16.2    | DSIref  | in pseudo code                                             | 180 |

|     |         |         | Main function of algorithm                                 | 180 |

|     |         | 16.2.2  | Creation of DSI types                                      | 180 |

|     |         |         | Propagation of DSI types                                   | 183 |

|     |         | 16.2.4  | Creation of DSI type combinations                          | 186 |

|     |         |         | Local type compatibility                                   | 187 |

|     |         |         | Global type compatibility                                  | 189 |

|     |         | 16.2.7  | Compute all type combinations                              | 190 |

|     |         |         | Compute all valid type combinations with nesting           | 191 |

|     | 16.3    | Compl   | exity of the DSIref algorithm                              | 195 |

| 17  |         |         | ng of sophisticated approach                               | 199 |

|     |         |         | mance                                                      | 199 |

|     | 17.2    |         | sion                                                       | 200 |

|     |         | 17.2.1  | Sophisticated versus naive combination                     | 201 |

|     |         |         | Type merging                                               | 201 |

|     |         |         | Shortcomings of the DSIcore algorithm                      | 203 |

|     |         |         | C++ and C examples and loss of perfect type information    | 204 |

|     |         |         | Strand length                                              | 205 |

|     |         |         | Data structure obfuscation                                 | 206 |

|     |         |         | False positives for nesting detection                      | 207 |

|     |         | 17.2.8  | Primitive type refinement                                  | 207 |

| 18  | Conc    | lusions |                                                            | 209 |

|     | _       | , .     |                                                            |     |

| Ш   |         |         | ons of dynamic data structure detection on source binaries | 215 |

|     | COC     | ie aliū | UIIIaiics                                                  | 213 |

| Bib | oliogra | aphy    |                                                            | 221 |

## **List of Tables**

| 1.1               | Methodology for answering the research questions (RQ) and challenges (Ch) stated in Sections 1.1 and 1.2 of this dissertation.                                                                                                                                                                                                                                 | xlii           |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3.1               | Overview of DDS detection tools                                                                                                                                                                                                                                                                                                                                | 17             |

| 4.1               | Results for artificial memory event and memory leak detection benchmark                                                                                                                                                                                                                                                                                        | 32             |

| 5.1               | Tabular view of relative offset calculations between strand connections as seen in Fig. 5.10: beginning of cells (starting with column $S_1$ ), between linkage offsets (starting with column $S_5$ ), beginning of cells to linkage offsets (starting with column $S_9$ ).                                                                                    | 56             |

| 6.1               | Symbols used in the temporal repetition algorithm                                                                                                                                                                                                                                                                                                              | 66             |

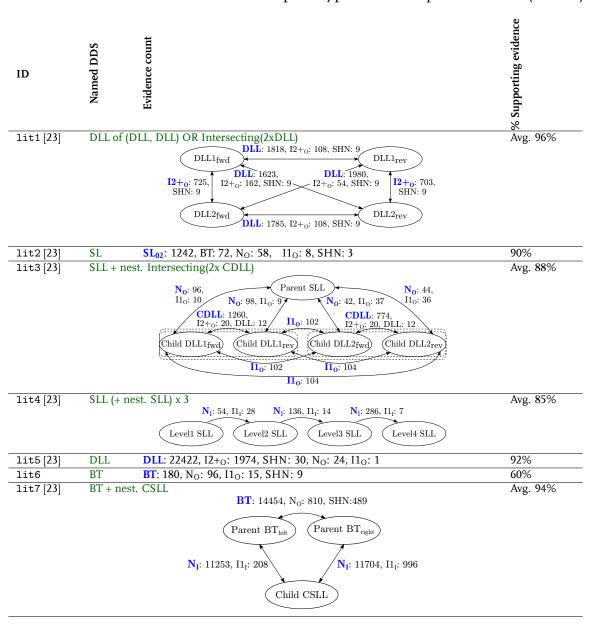

| 8.1<br>8.2<br>8.3 | Benchmarks (Part I) (see Table 8.2 for Part II of the benchmarks) Benchmarks (Part II) (see Table 8.1 for Part I of the benchmarks) Additional benchmarks that test either previously untested DS or different programming constructs (tests where DSI detects the underlying DS but not it's semantics, e.g., stack or queue, are denoted with $\checkmark$ ) | 95<br>96<br>97 |

| 8.4               | Results obtained from the prototypical DSI implementation (Part I)                                                                                                                                                                                                                                                                                             | 98             |

| 8.5               | Results obtained from the prototypical DSI implementation (Part II)                                                                                                                                                                                                                                                                                            | 99             |

| 8.6               | Results obtained from the prototypical DSI implementation (Part III)                                                                                                                                                                                                                                                                                           | 100            |

| 10.1              | Overview of the analysed malware, including which malware is based upon each other (if applicable) and which components are reused (only with regards to the DS of interest to DSI/DSIbin)                                                                                                                                                                     | 134            |

| 12.1              | Overview of type recovery tools: the analysis can be static, dynamic or both; the input is either binary code or a memory snapshot; features marked with a ? are not clear from the literature                                                                                                                                                                 | 144            |

| 15.1              | Results obtained from the prototypical DSIbin implementation                                                                                                                                                                                                                                                                                                   | 172            |

## **List of Figures**

| 1.1  | Three level skip list with one node per level and all nodes are of |         |

|------|--------------------------------------------------------------------|---------|

|      | the same type                                                      | xxxii   |

| 1.2  | DSI's memory abstraction shown for the Linux kernel list. DSI      |         |

|      | detects two connected (cyclic) singly linked list (atomic building |         |

|      | blocks of a DS, shown with colored arrows) that form the cyclic    |         |

|      | doubly linked list by being connected in reverse order. Addi-      |         |

|      | tionally, the singly linked lists run through nodes of different   |         |

|      | types, illustrating that DSI allows that a DS node only covers     |         |

|      | a subregion (dashed boxes) of the same type of the allocated       |         |

|      | memory chunk (outermost solid boxes). Figure is reproduced         |         |

|      | from our publication [94]                                          | xxxiii  |

| 1.3  | A singly linked list with two doubly linked list children. The     |         |

|      | singly linked lists forming the atomic building blocks of the DS   |         |

|      | are shown with colored arrows. The right child doubly linked       |         |

|      | list is in a degenerate shape due to a pending insertion of the    |         |

|      | last element                                                       | xxxiv   |

| 1.4  | A parent singly linked list with two nested doubly linked list     |         |

|      | children                                                           | XXXV    |

| 1.5  | Types for the VNC clipping library as found in the source code,    |         |

|      | as recovered by Howard and as refined by DSIbin (left), and the    |         |

|      | corresponding VNC data structure (right)                           | xxxviii |

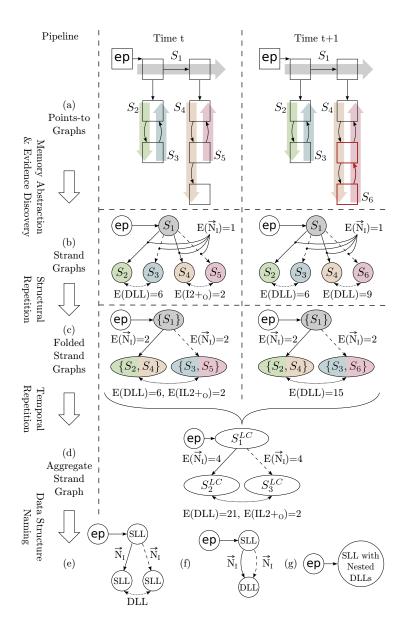

| 2.1  | Overview of DSI, reproduced from our publication [107]             | 5       |

| 4.1  | Freeing memory with incoming/outgoing pointers, with all en-       |         |

|      | try pointers (ep) omitted except for the freed memory              | 20      |

| 4.2  | C code performing an allocation of an integer on the heap          | 30      |

| 4.3  |                                                                    | 30      |

| 4.4  | Source code excerpt of leak7 [27]                                  | 33      |

| 4.5  | Source code excerpt of leak8 [28]                                  | 35      |

| 4.6  | stackoverflow.com example, step 6826                               | 37      |

| 4.7  | stackoverflow.com example, step 6830                               | 38      |

| 4.8  | stackoverflow.com example, step 6831                               | 39      |

| 4.9  | stackoverflow.com example, step 6836                               | 40      |

| 4.10 | stackoverflow.com example, step 6837                               | 41      |

| 4.11 | stackoverflow.com example, step 6842                               | 42      |

xx List of Figures

| 4.12       | stackoverflow.com example, step 6843                                                                                                                                                          |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

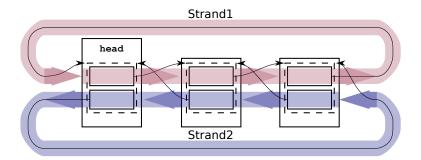

| 5.1        | Parent child nesting, with two child Linux kernel lists running through a common parent node. Figure reproduced from our                                                                      |

|            | publication [107]                                                                                                                                                                             |

| 5.2        | DSI's memory abstraction shown for the Linux kernel list. DSI detects two connected (cyclic) singly linked lists that form the cyclic doubly linked list by being connected in reverse order. |

|            | Figure is reproduced from our publication [94]                                                                                                                                                |

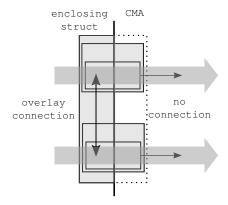

| 5.3        | The maximum enclosing memory sub-region in case of a sur-                                                                                                                                     |

|            | rounding struct (solid line on the left) and a custom memory                                                                                                                                  |

|            | allocator (dotted line on the right) highlighted in grey. The                                                                                                                                 |

|            | strands are indicated as block arrows and the resulting overlay                                                                                                                               |

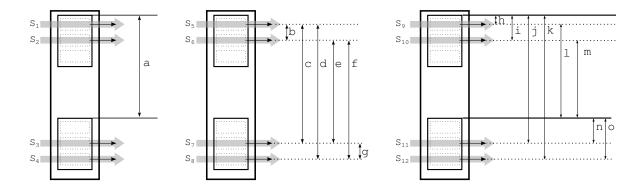

| <b>-</b> 4 | connection as a bidirectional arrow                                                                                                                                                           |

| 5.4        | Overlay connection between the most upstream cell of a strand                                                                                                                                 |

|            | with multiple cells per vertex and another strand with only one                                                                                                                               |

| 5.5        | cell per vertex                                                                                                                                                                               |

| 3.3        | tive offsets of the overlay connections                                                                                                                                                       |

| 5.6        | Strands with changed offsets between them                                                                                                                                                     |

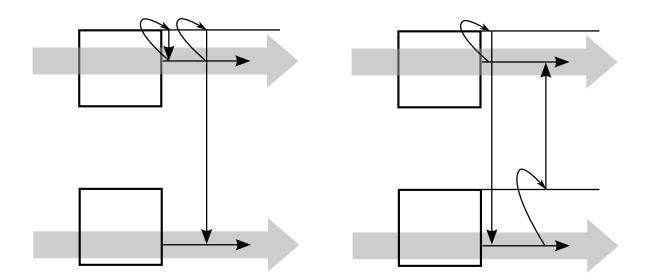

| 5.7        | Parent child relation on indirect nesting, with parent strand                                                                                                                                 |

| ٠,,        | changing position within vertices. Child strands are indicated                                                                                                                                |

|            | with two vertical grey arrows only, without cells or vertices                                                                                                                                 |

| 5.8        | Parent child relation on overlay nesting, with child strands chang-                                                                                                                           |

|            | ing position within vertices. Child strands are only indicated                                                                                                                                |

|            | with two vertical grey arrows, without further cells besides the                                                                                                                              |

|            | head cell                                                                                                                                                                                     |

| 5.9        | Strands switching positions within vertices                                                                                                                                                   |

| 5.10       | Relative offset calculations between strand connections: begin-                                                                                                                               |

|            | ning of cells (left), between linkage offsets (middle), beginning                                                                                                                             |

|            | of cells to linkage offsets (right).                                                                                                                                                          |

| 5.11       | Two possible implementations shown for calculating the rela-                                                                                                                                  |

|            | tive offsets between two strands in an overlay connection. On                                                                                                                                 |

|            | the left the offset calculation always starts from the start address                                                                                                                          |

|            | of the cell of the top strand to the linkage offset of both strands.                                                                                                                          |

|            | On the right the calculation is performed once from the start                                                                                                                                 |

|            | address of the cell of the top strand and once from the start                                                                                                                                 |

|            | address of the lower strand                                                                                                                                                                   |

List of Figures xxi

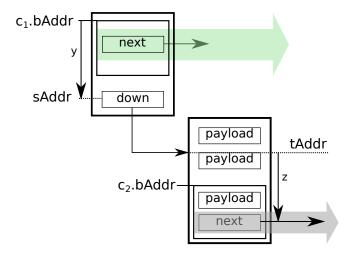

| 5.12       | Memory offsets used for computing an indirect strand connection. $c_1$ . <b>bAddr</b> marks the start address of the the first cell, and $c_2$ . <b>bAddr</b> the start address of the second cell. <b>sAddr</b> is the source address of the outgoing pointer and <b>tAddr</b> is the target address where the pointer points to | 61       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.13       | Relative offsets for an indirect strand connection both on the source (top vertices) and the target side (bottom vertex). The parent strand (source) switches position within a vertex without changes in the relative offsets (between parent strand and outgoing pointer).                                                      | 62       |

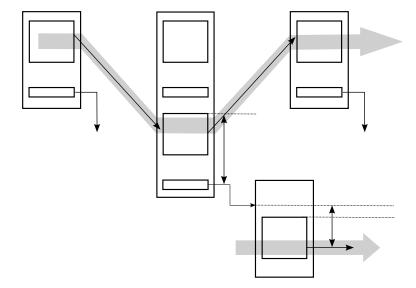

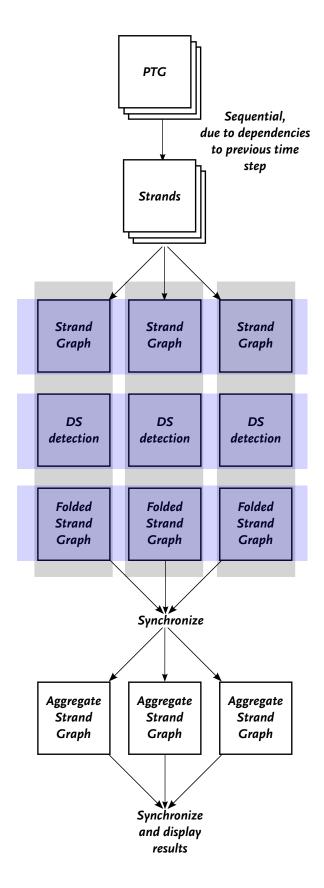

| 7.1<br>7.2 | Overview of DSI with respect to sequential/parallel execution Hot-spot analysis of example binary-trees-debian (sequential ex-                                                                                                                                                                                                    | 76       |

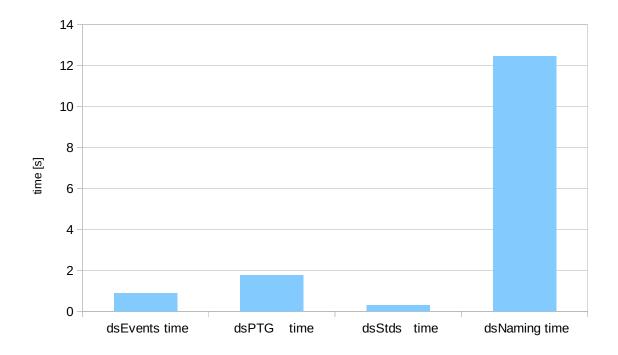

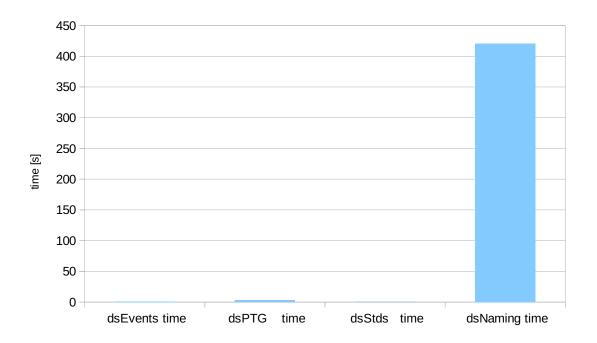

| 7.3        | ecution)                                                                                                                                                                                                                                                                                                                          | 80<br>81 |

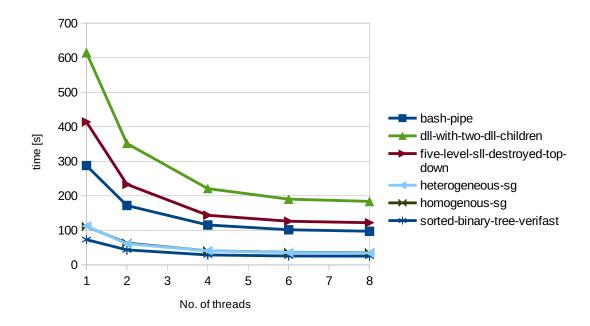

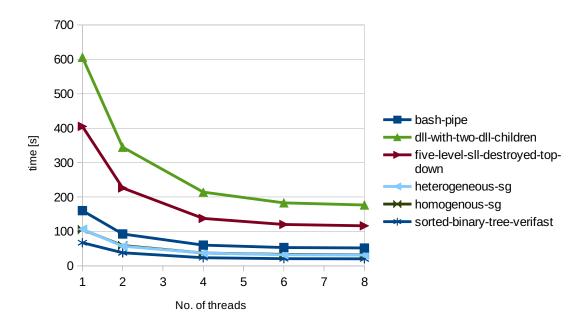

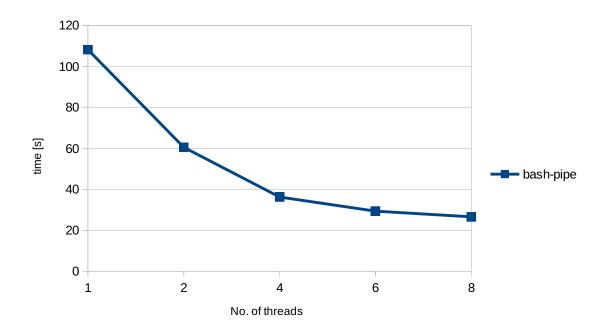

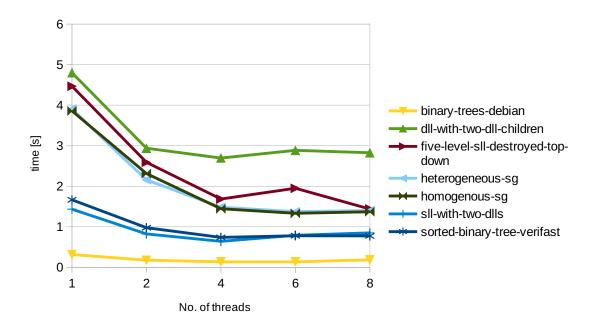

| 7.4        | Laptop: Total runtimes for long running examples                                                                                                                                                                                                                                                                                  | 83       |

| 7.5        | Laptop: Total runtimes for short running examples                                                                                                                                                                                                                                                                                 | 83       |

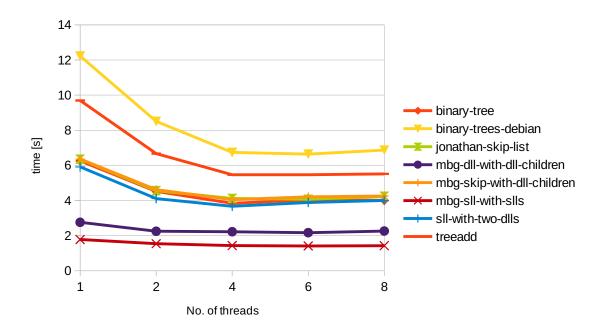

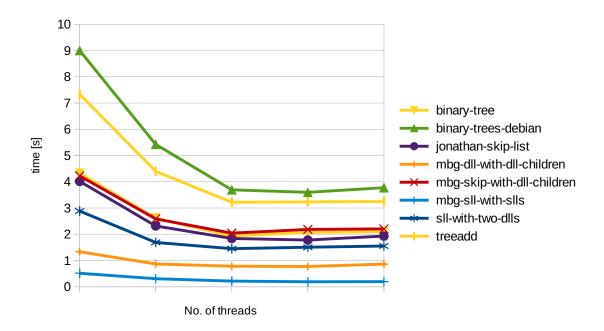

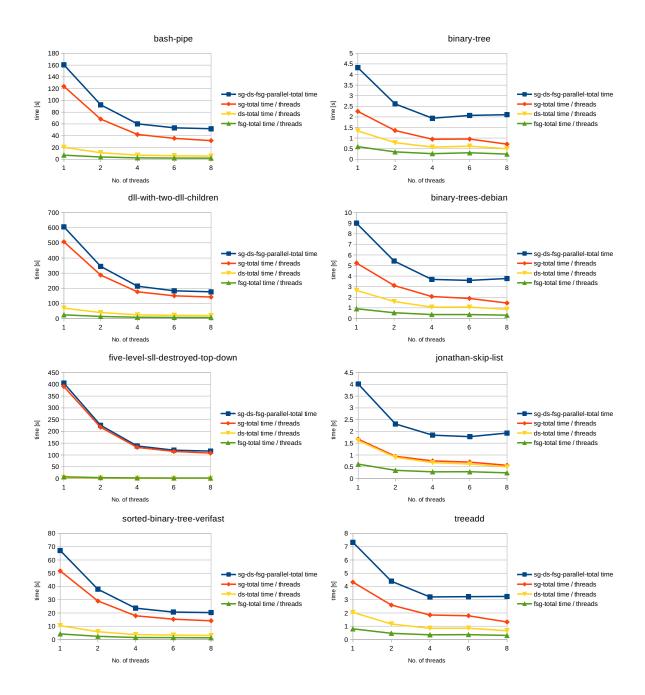

| 7.6        | Laptop: Runtimes for strand graph, DS detection and folded strand graph creation for the long running examples                                                                                                                                                                                                                    | 84       |

| 7.7        | Laptop: Runtimes for strand graph, DS detection and folded strand graph creation for the short running examples                                                                                                                                                                                                                   | 85       |

| 7.8        | Laptop: Runtime for the longest running aggregated strand graph creation of the benchmark (bash-pipe example)                                                                                                                                                                                                                     | 86       |

| 7.9        | Laptop: Runtimes for short running aggregated strand graph creations. This chart combines both long and short running examples of Figs. 7.4 and 7.5; note that the aggregated strand                                                                                                                                              |          |

| 7.10       | graph runtimes are equally short for most of the examples Laptop: Details of runtimes for the strand graph, DS detection and folded strand graph creation, both for a selection of long (left) and short (right) running examples                                                                                                 | 86<br>88 |

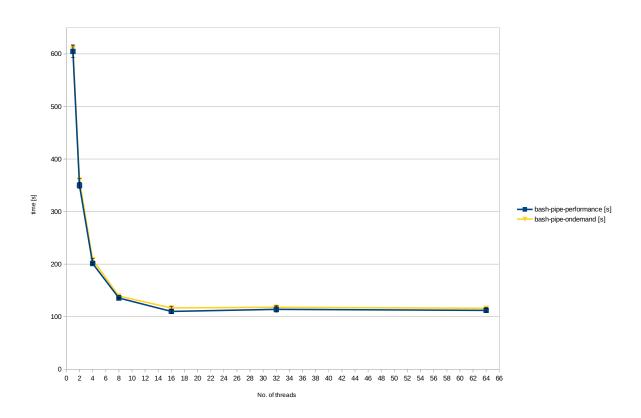

| 7.11       | Computebox: Example bash-pipe with two governor strategies                                                                                                                                                                                                                                                                        |          |

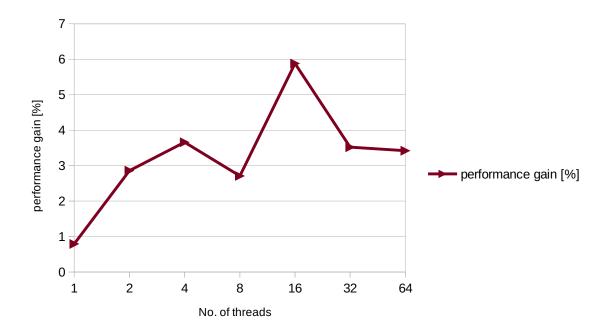

| 7.12       | for scaling the CPU frequency: ondemand and performance Computebox: Performance gains (in percent) for the bash-pipe example between the Linux kernel performance governor and the ondemand governor                                                                                                                              | 90<br>91 |

| 8.1        | Source code excerpt of lit3 [23] with the Linux kernel list macros and dead code sections removed. Manually adjusted number of elements are indicated by comments                                                                                                                                                                 | 105      |

xxii List of Figures

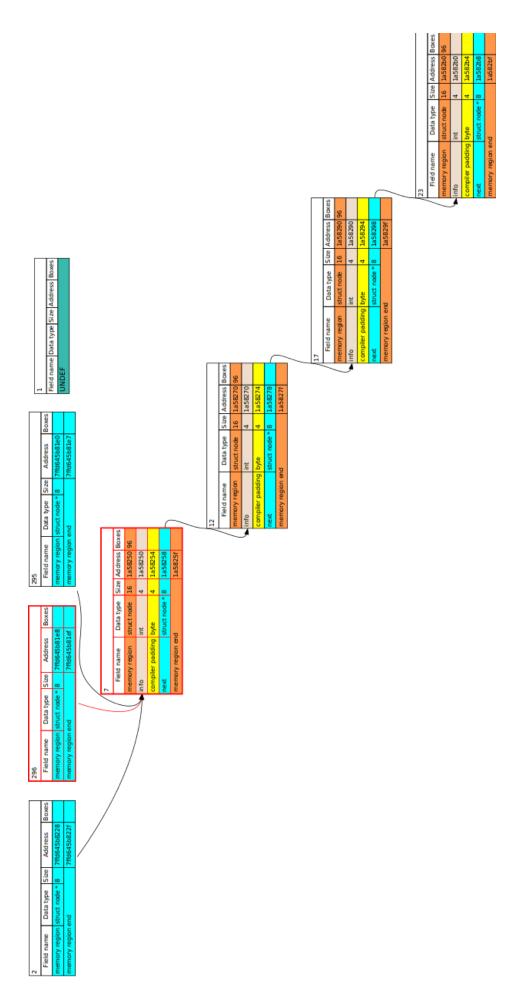

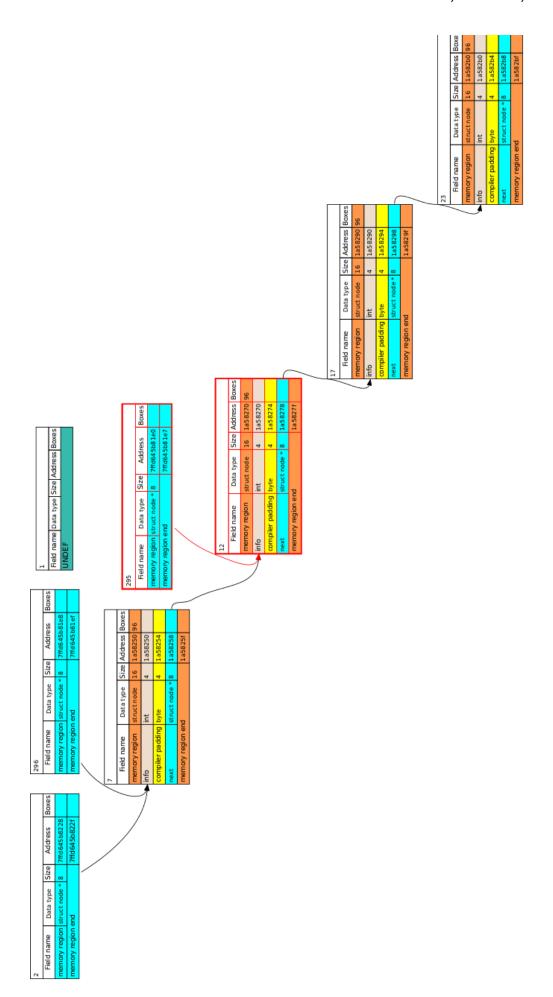

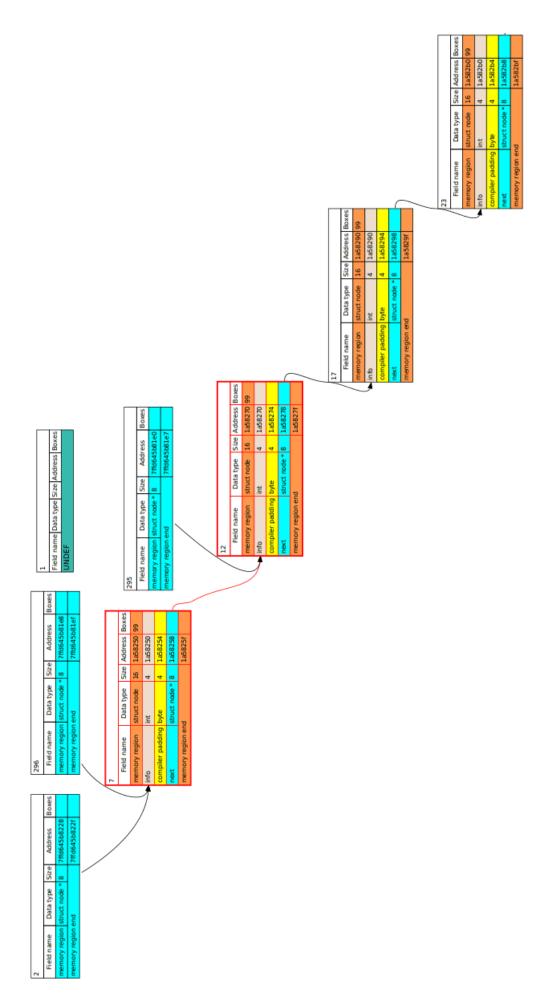

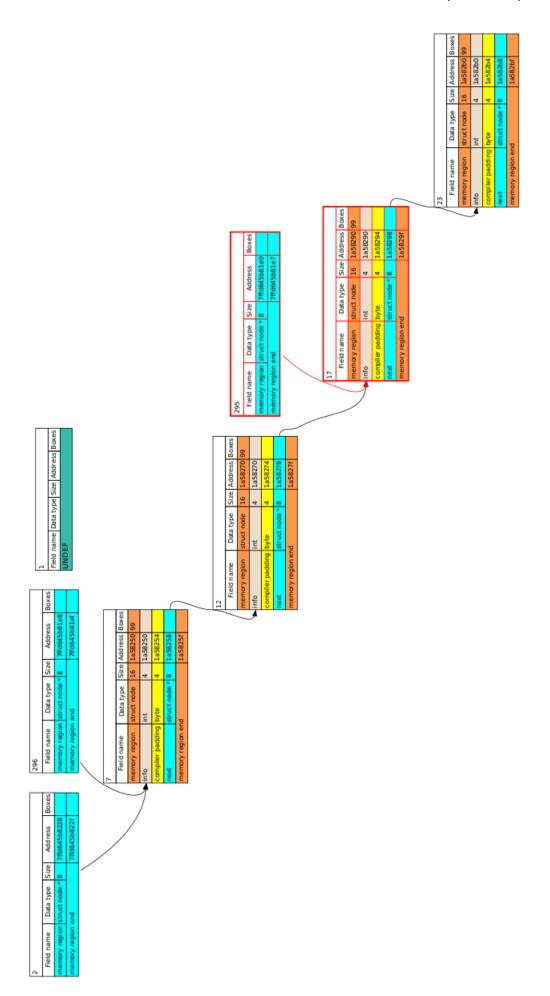

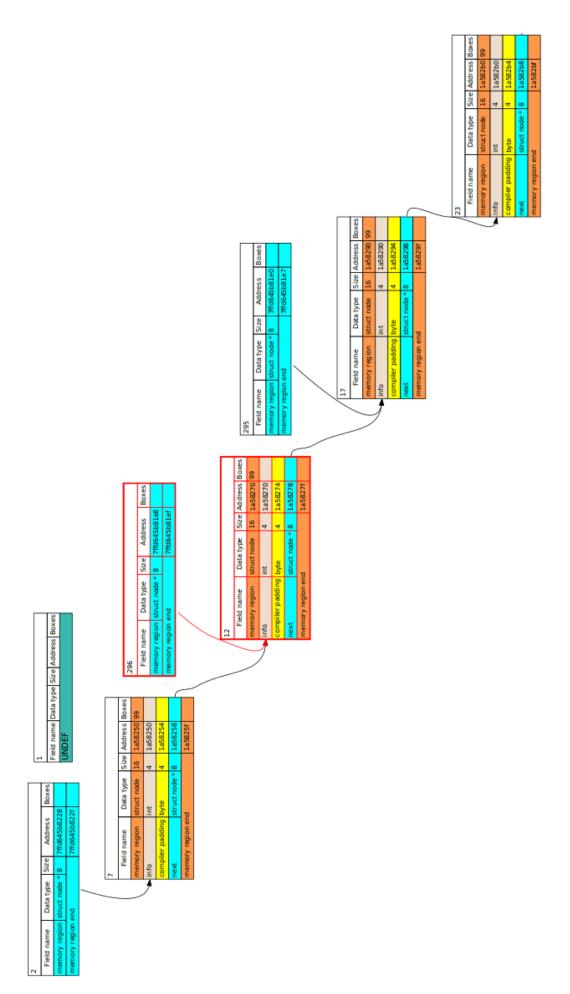

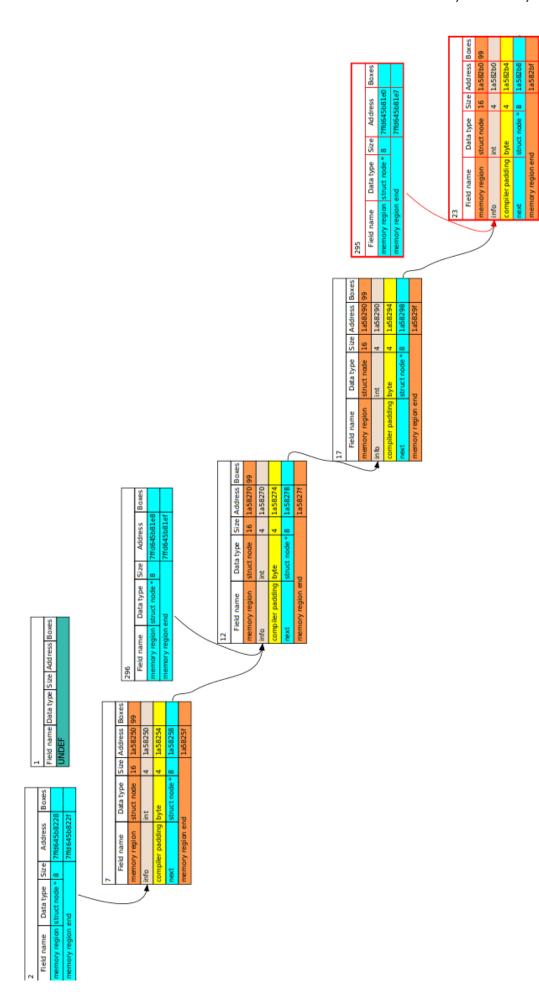

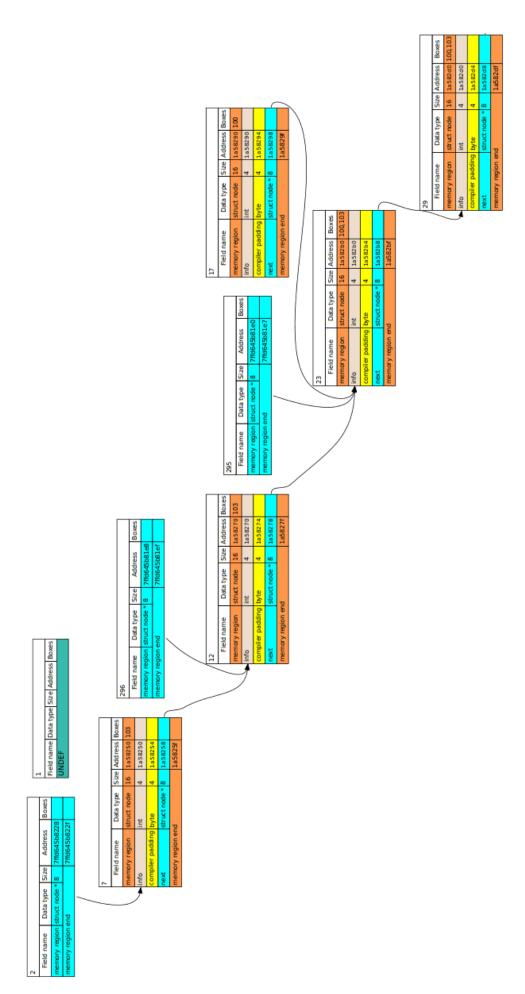

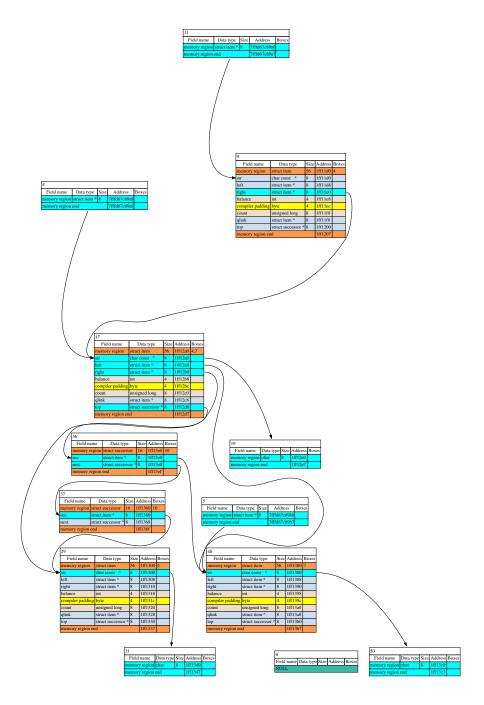

| 8.2  | A points-to graph for one time step, when running tsort. The binary tree nodes are formed by struct item nodes, the singly linked list is formed on struct successor nodes. Blue nodes are pointers into the data structure. Moreover, blue nodes referenced by the data structure (by field str of struct item) are abstracted char arrays. structs are indicated by orange fields marking the start and end of the struct memory region. Pointer members of a struct are colored as follows: (i) uninitialized pointers are grey; (ii) pointers pointing to valid memory are blue. Paddings added by the compiler are yellow. The remaining primitive types are colored pinkish | 112        |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

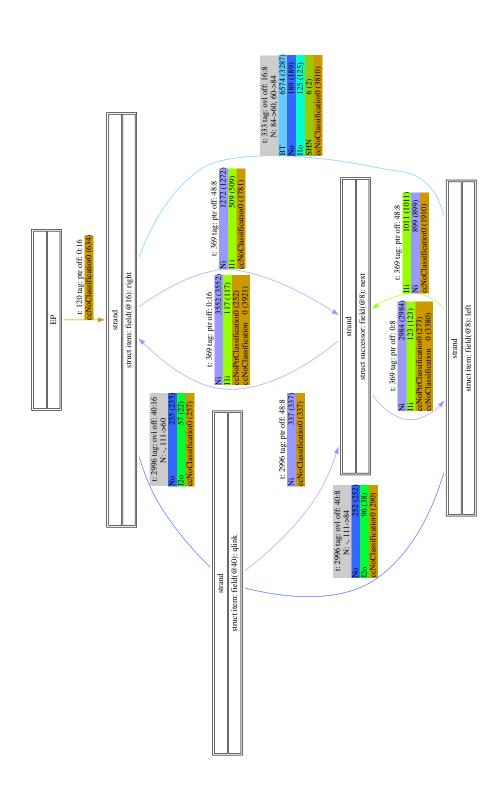

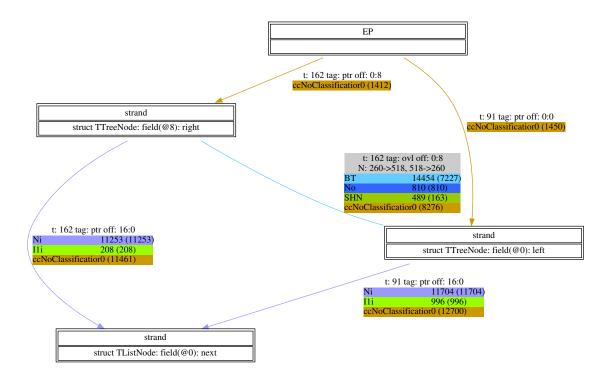

| 8.3  | The aggregated strand graph for tsort, with an ambiguous nesting relation between the binary tree strands (left/right fields of type struct item) and the struct successor singly linked list                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 118        |

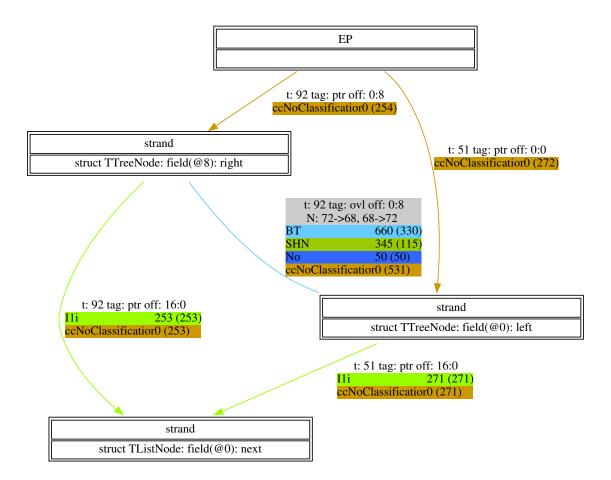

| 8.4  | lit7 [23]: DSI's aggregated strand graph showing the BT label for the parent and the $I1_I$ label for the child element, which hints at a different implementation of the test case than has been expected: not every binary tree node has a nested cyclic singly linked list                                                                                                                                                                                                                                                                                                                                                                                                     | 119        |

| 8.5  | lit7 [23]: DSI's aggregated strand graph showing the BT label for the parent and the expected $N_I$ label for the child elements, after modifying the initial test case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 120        |

| 8.6  | Source code excerpt from example tree-with-cslls taken from Predator [23], with modifications done to control the number of created elements. In addition the code section responsible for the creation of a child cyclic singly linked list for each binary tree node has been changed from the original example which created a child cyclic singly linked list only for the first node in the tree.                                                                                                                                                                                                                                                                            | 121        |

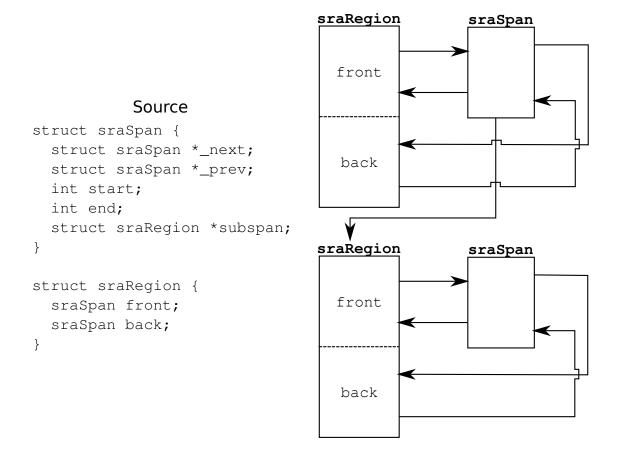

| 10.1 | The source code of the VNC clipping library doubly linked list on the left and an example instantiation on the right (figure adopted from our publication [94])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 135        |

|      | A Linux kernel list implementation with type information (top) and without type information (bottom)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 138        |

| 11.3 | type information (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 139<br>139 |

List of Figures xxiii

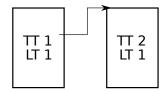

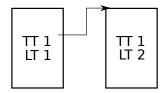

| 11.4 | Identical true type as given by source code versus differently inferred logical type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

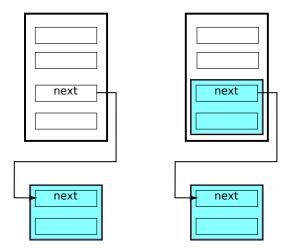

| 11.5 | Memory chunks with a parent (big chunks at the top) child (blue chunks) relation. On the left, no nested child element inside the parent is present; on the right, a nested child element inside the parent is present                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

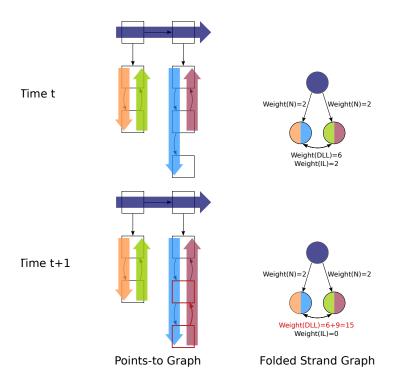

| 12.1 | Temporal repetition between time step $t$ and $t+1$ used to outnumber the degenerate shape of the child double linked list at time step $t$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

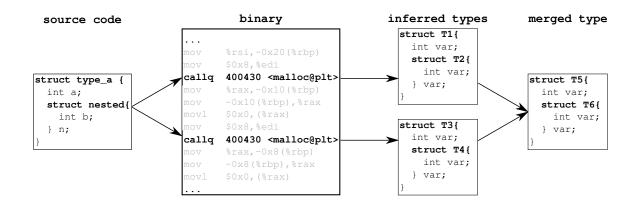

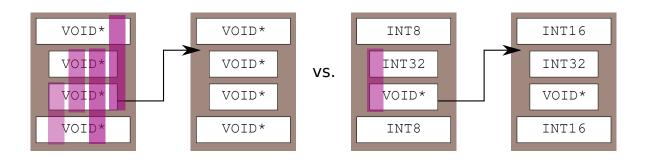

| 14.1 | Type merging in binaries (figure reproduced from talk at ASE2017 on [94])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

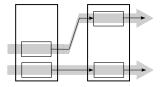

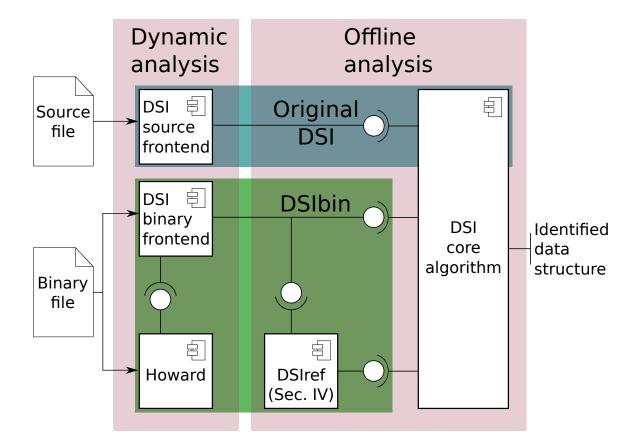

| 14.2 | Overview of our DSIbin tool chain (figure reproduced from our publication [94])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

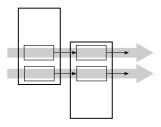

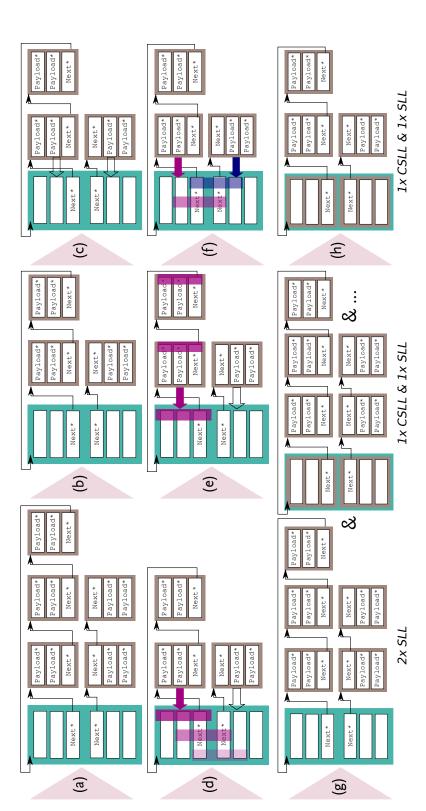

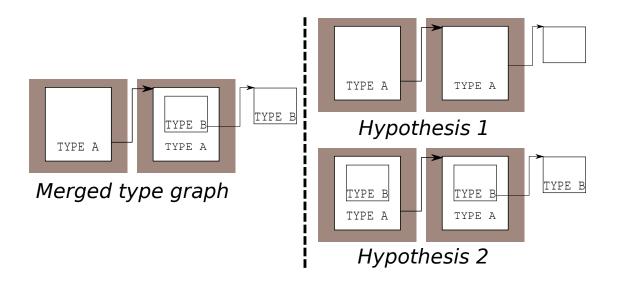

| 16.2 | Overview of the DSIref approach: (a) create sequence of points-to-graphs from program execution (only one shown); (b) construct merged type graph capturing pointer connections between types; (c) exploit pointer connections by mapping type subregions (two possibilities shown); (d) observe that multiple interpretations may be possible; (e) propagate each interpretation along pointer connections; (f) rule out inconsistencies; (g) evaluate remaining interpretations via DSI; (h) choose the 'best' interpretation in terms of DS complexity (indicated by merged type graph with resulting label <i>1x CSLL &amp; 1x SLL</i> ). Figure reproduced from our publication [94] |

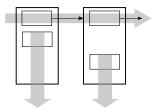

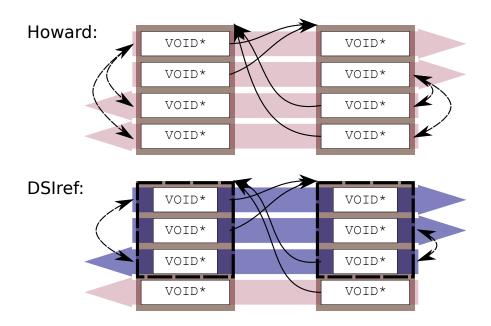

| 17.1 | Two doubly linked lists running in parallel, showing the possible strand combinations for the types inferred by Howard (top) and by DSIref (bottom). Figure reproduced from our publication [94]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# List of Algorithms

| 1  | Main part of memory leak detection                                                                                                                                         | 25  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Calculation of the initial set of vertices on which the recursive                                                                                                          |     |

|    | memory leak detection algorithm operates                                                                                                                                   | 26  |

| 3  | Memory leak detection on the outgoing edges                                                                                                                                | 27  |

| 4  | Search for a static vertex on incoming edges                                                                                                                               | 28  |

| 5  | Calculation of all edges that point into the leaked memory and that need to be removed                                                                                     | 28  |

| 6  | Calculation of all edges that point outwards from the leaked memory.                                                                                                       | 29  |

| 7  | Creation of artificial memory events to cut incoming and outgoing edges to a freed/leaked memory and to remove leaked vertices                                             | 29  |

|    | veruces                                                                                                                                                                    | ZJ  |

| 8  | Calculation of the strand graph vertices and edges for a time step                                                                                                         | 57  |

| 9  | Calculation of the overlay connection configurations                                                                                                                       | 59  |

| 10 | Calling the classification routine on configuration sets. Addi-                                                                                                            |     |

|    | tionally, the edges are being stored                                                                                                                                       | 59  |

| 11 | Calculation of the indirect strand connections                                                                                                                             | 63  |

| 12 | Main part of DSI's data structure detection algorithm, including the strand graph creation, the naming of the data structures, and the structural and temporal repetitions | 67  |

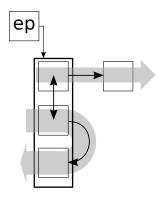

| 13 | Computation of an aggregated strand graph from the point of view of a given entry pointer $(ep)$                                                                           | 68  |

| 14 | Recursive alignment of the aggregated strand graph and folded strand graph for computing a common subset of both graphs .                                                  | 70  |

| 15 | Computation of new elements inside of the folded strand graph                                                                                                              | 72  |

| 16 | Calculation of additions to the aggregated strand graph                                                                                                                    | 73  |

| 17 | Main part of the DSIref algorithm                                                                                                                                          | 181 |

| 18 | Calculate the possible DSI Types for an edge (part 1)                                                                                                                      | 182 |

| 19 | Calculate the possible DSI Types for an edge (part 2)                                                                                                                      | 182 |

| 20 | Recursive propagation of a DSI type along pointer connections                                                                                                              | 184 |

| 21 | Test whether type can be propagated to target vertex                                                                                                                       | 185 |

| 22 | Test if type can be propagated to source vertex                                                                                                                            | 186 |

| 23 | Calculation of the possible type combinations                                                                                                                              | 187 |

xxvi List of Algorithms

| 24 | Check local compatibility of type instances                     | 188 |

|----|-----------------------------------------------------------------|-----|

| 25 | Calculate compatibility of types                                | 189 |

| 26 | Conducting a global compatibility check of the types            | 190 |

| 27 | Create all valid combinations of types, such that each hypothe- |     |

|    | sis contains the maximal amount of possible type combinations   | 191 |

| 28 | Check global compatibility of nested types                      | 192 |

| 29 | Collect all nested types                                        | 192 |

| 30 | Collect and group all nested type instances                     | 193 |

| 31 | Create the type combinations                                    | 194 |

|    |                                                                 |     |

#### **Acronyms**

ABI Application Binary Interface.

**AFE** Artificial Free Event.

**AME** Artificial Memory Event.

**ASG** Aggregated Strand Graph.

AUE Artificial Undef Event.

**BT** Binary Tree.

**CDLL** Cyclic Doubly Linked List.

**CIL** C Intermediate Language.

CMA Custom Memory Allocator.

coreutils GNU Core Utilities.

**CPU** Central Processing Unit.

**CSLL** Cyclic Singly Linked List.

**DDoS** Distributed Denial of Service.

**DDS** Dynamic Data Structure.

**DDS** Dynamic Data Structure.

**DDT** Data-structure Detection Tool.

**DFG** Deutsche Forschungsgemeinschaft.

**DgS** Degenerate Shape.

**DLL** Doubly Linked List.

**DSI** Data Structure Investigator.

**DSIbin** Data Structure Investigator for Binaries.

**DSIcore** Data Structure Investigator Core Algorithm.

xxviii Acronyms

**DSIref** Data Structure Investigator Refinement Component.

**DSIsrc** Data Structure Investigator for Source Code.

**DSItype** DSI Type.

dsOli Data Structure Operation Location and Identification.

**EP** Entry Pointer.

FSG Folded Strand Graph.

FV Formal Verification.

**HT** Hyper Threading.

JVM Java Virtual Machine.

LKL Linux Kernel List.

LOC Lines of Code.

LT Logical Type.

**ME** Memory Event.

MER Maximum Enclosing memory sub-Region.

**MTG** Merged Type Graph.

**PC** Program Comprehension.

**PTG** Points-to Graph.

**RAM** Random Access Memory.

**RE** Reverse Engineering.

**SC** Strand Connections.

**SG** Strand Graph.

**SIG** Signature Generation.

**SL** Skip List.

**SLL** Singly Linked List.

**StS** Stable Shape.

Acronyms xxix

**TT** True Type.

VIS Visualization.

**VLS** Variable Leaving Scope.

**X.Org** Open source X Window System implementation.

**XSD** XML Schema Definition.

#### 1 Introduction

This dissertation is primarily concerned with the reverse engineering of pointer based Dynamic Data Structures (DDSs) in *C/C++ binaries*, such as doubly linked lists or trees. The pressing needs to analyse programs for which source code is unavailable are manifold. A company might lose its data – as has happened, e.g., for SEGA's "Magic Knight Rayearth" [1, 37] – but does not want to completely lose the engineering effort put into a software. A customer might be forced to maintain a closed source program after it has reached its end-of-life and need to develop, e.g., security patches [99]. In addition, the constantly growing amount of malware [17] requires security specialists to gain an understanding of malware behaviour.

As DDSs are a fundamental aspect of many programs, it is important to have information about the therein employed DDSs when conducting reverse engineering. When knowing the DDS shape one already has an idea of the corresponding data structure manipulating code sections – e.g., an insert into a Doubly Linked List (DLL) requires to set at least the previous and next pointers instead of only the next pointer for an insert into a Singly Linked List (SLL) – and possibly even about the overall algorithm – e.g., consider a code section performing a search that uses a Binary Tree (BT) versus a Singly Linked List (SLL). The detection of such DDSs is pursued by the recent DSI¹ approach.

While there already exist Dynamic Data Structure (DDS) identifi-Related work. cation tools for binaries, with DDT [74], ARTISTE [49] and MemPick [69] being state-of-the-art examples, they have limitations such as regarding recognition precision or due to strong assumptions. For example, DDT relies on the presence of well-defined interface functions, which is suitable when, e.g., the C++ STL library [91] is used in the programs under analysis. But this assumption is not satisfied for customized DDSs or in the presence of low-level optimizations such as inlining or macro based interfaces. ARTISTE looses its precision in the face of degenerate shapes, which occur during DDS manipulation operations. MemPick cuts connections between data structure nodes, which for now correspond to the allocated memory for one element of the DDS, of different types. This prevents MemPick to handle DDSs running through nodes of different types, for which the Linux Kernel List (LKL) [15] is a prominent example. DDT and ARTISTE also do not handle the Linux Kernel List (LKL), and all three tools struggle with complex parent child relations such as arbitrary nesting levels, i.e., where the children of a

<sup>&</sup>lt;sup>1</sup>SWT Research Group, University Bamberg, DFG-Project LU 1748/4-1

xxxii 1 Introduction

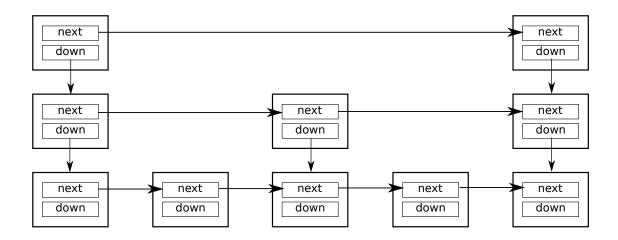

Figure 1.1: Three level skip list with one node per level and all nodes are of the same type.

parent child relation can have children of their own and which is not limited to a certain depth. Additionally, tools based on shape analysis [81] exists, which is concerned with statically inferring and verifying data structure shapes and their invariants. Therefore recent shape analysis tools such as Predator [65] and Forester [72] are of interest to us, though their main difference to DSI is their static analysis approach that is more conservative than a dynamic analysis [74,81]. Forester handles (cyclic) SLLs and Doubly Linked Lists (DLLs), the LKL, trees and skip lists in sequential non-recursive C programs, whereas DSI also works for recursive C programs. Predator's focus lies on DLLs, especially the LKL, and SLLs. Other recursive data structures like trees, which are supported by DSI, are currently out of scope for Predator.

The limitations of related work are addressed with the DSI goals & approach. novel DSI approach [107], authored by Dr. White in the context of the Deutsche Forschungsgemeinschaft (DFG) project "Learning Data Structure Behaviour from Executions of Pointer Programs" (LU 1748/4-1). DSI requires C source code to enable its dynamic analysis, where a concrete execution of a program is precisely analysed; this is in contrast to a static analysis which conservatively reasons about all possible executions of a program [66]. In particular, DSI increases the analysis precision for and the scope of detectable DDSs, such as Skip Lists (SLs) and arbitrary parent child nestings. An SL provides fast search capabilities by providing multiple hierarchical segmented levels on top of a sorted list as shown in Fig. 1.1. The level segments store information about the underlying list elements reachable from a segment, which is used to either skip to the next segment if the searched token cannot be found in the current segment or move down the next lower level to repeat searching segments until the searched token is either found in the bottom list or is not contained at all. Additionally, DSI makes few assumptions, e.g.,

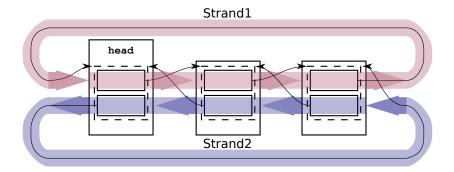

Figure 1.2: DSI's memory abstraction shown for the Linux kernel list. DSI detects two connected (cyclic) singly linked list (atomic building blocks of a DS, shown with colored arrows) that form the cyclic doubly linked list by being connected in reverse order. Additionally, the singly linked lists run through nodes of different types, illustrating that DSI allows that a DS node only covers a subregion (dashed boxes) of the same type of the allocated memory chunk (outermost solid boxes). Figure is reproduced from our publication [94].

it does not require the presence of interface functions or that a memory chunk, i.e., memory allocated on the stack or heap, corresponds to a DDS node as a whole. These properties of DSI have their foundations in the rich type information found in source code and make DSI highly interesting for automated DDS discovery.

DSI functions by first instrumenting the source code with the C Intermediate Language (CIL) framework [88] to capture memory changing events, such as memory (de-)allocations and pointer writes. The instrumented program is then executed and an event trace recorded. Finally the event trace is analysed offline by DSI resulting in a named DDS. DSI sets itself apart from related work by the following novelties:

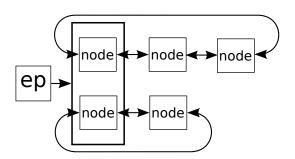

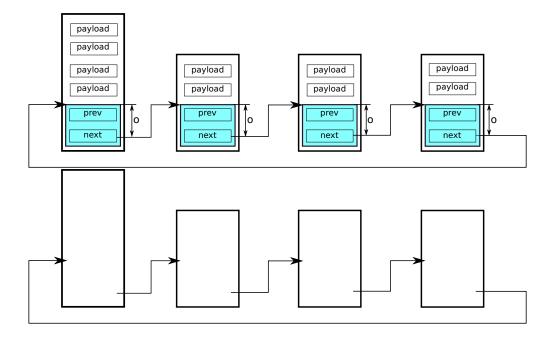

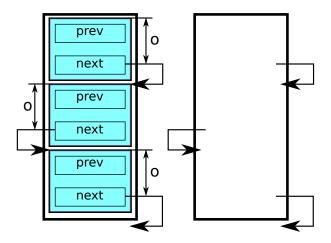

**Novel memory abstraction.** DSI uses a novel memory abstraction to represent the heap/stack state, i.e., the allocated memory and the pointers connecting them, which allows us to handle data structures such as the LKL, SLs, and arbitrary nesting scenarios. Our memory abstraction is guided by the observation that a DDS is composed of various SLLs as their atomic building blocks, termed *strands*, and their interconnections, termed *Strand Connections (SC)*, as can be seen in Fig. 1.2. The LKL shown therein is composed of two strands, one for each direction, and the two strands are connected in a reverse order. Additionally, the nodes of an SLL are allowed to cover smaller subregions of memory, termed *cells*, which can either be a complete struct or only a nested struct. This seamlessly covers DDSs in the style of the LKL.

**Degenerate shapes.** DSI takes Degenerate Shapes (DgSs) into account instead of avoiding them [69, 74, 106]. DgSs occur due to DDS manipulation operations, where the properties of the true Stable Shape (StS) of a DDS are broken, as shown

xxxiv 1 Introduction

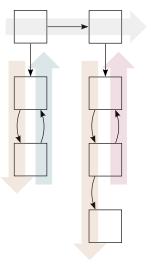

Figure 1.3: A singly linked list with two doubly linked list children. The singly linked lists forming the atomic building blocks of the DS are shown with colored arrows. The right child doubly linked list is in a degenerate shape due to a pending insertion of the last element.

in Fig. 1.3 where one child DLL is in a DgS due to an unfinished insert operation. DSI does so by gathering evidence for the true StS for a DDS during its analysis. **Data structures and their naming.** DSI creates a named output of the DDS pointed to by a given entry pointer of the program under analysis, e.g., "Binary tree with nested singly linked list children". DSI currently supports the following data structures: (cyclic) singly linked lists and doubly linked lists, skip lists, binary trees and arbitrary combinations of those DDSs in the form of parent child nesting. Skip lists and the nesting are not covered by [49, 69, 74].

# 1.1 Source code: Research question and challenges

This dissertation first contributes to improving upon the state-of-the-art of [49,69, 74], by realizing the DSI approach on source code. This results in a research tool for automatically detecting and naming DDSs and allows us to answer the first research question:

**Research Question 1:** Is the DSI approach adequate to reach its goals of automatically detecting dynamic data structure shapes with high precision in the presence of degenerate shapes and, in particular, how far must the DSI concept be refined in order to deal with the wealth of dynamic data structure implementations employed in real-world software?

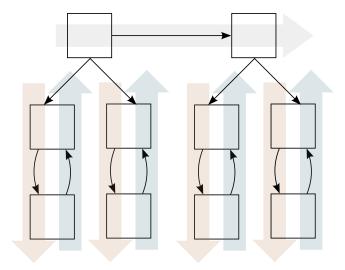

Figure 1.4: A parent singly linked list with two nested doubly linked list children.

The first part of the question will be answered positively by us by carrying out a diverse benchmark including real world examples (libusb [13], bash [10]) and examples taken from the shape analysis literature [65,72] on the realized DSI approach. Along the way, various problems are resolved within this dissertation, such as quantifying the interconnections of the atomic building blocks of DSI's memory abstraction forming a DDS and guaranteeing the consistency of the chosen abstractions. DSI uses graphs for representing its various employed memory abstractions; it is vital to keep those graphs consistent during the analysis. The foundation for DSI is the current heap state, captured by a Points-to Graph (PTG), where vertices are memory chunks and edges are pointers. Additional abstractions, i.e., as strands, the Strand Graph (SG), the Folded Strand Graph (FSG), and the Aggregated Strand Graph (ASG), are layered upon the Points-to Graph (PTG) and are further discussed in Ch. 2. Therefore a PTG needs to be kept consistent during memory manipulations and programming errors like memory leaks, leading to the first challenge:

**Challenge 1.1:** Can DSI's graph abstractions be kept consistent in the face of common memory events such as memory (de-)allocations, pointer writes and even programming errors?